近日,中国最大、世界第三大封测公司长电科技宣布,XDFOI Chiplet工艺已经实现了突破,并开始逐步进入稳定量产阶段,同步实现国际客户4nm节点多芯片系统集成封装产品出货,最大封装体面积约为1500mm2的系统级封装。该公司所研发的高密度多维异构集成系列工艺可以在有限的面积内,实现高密度的工艺集成,从而让芯片的封装尺寸更小,且性能更强。

众所周知,国内工业化起步较晚,在一些先进设备和技术上落后于西方等先进国家,尤其是在芯片制造领域,EUV光刻机是限制我国先进制程芯片发展的关键。不过当芯片制造进入3nm制程后,摩尔定律就越来越难以突破,加之半导体设备的技术竞争激烈,光刻机等设备价格与制造成本皆快速飙高,让业界被迫寻找新的替代技术,小芯片就是其中一个重要方向,同时也是中国市场换道超车的重要技术路径之一。

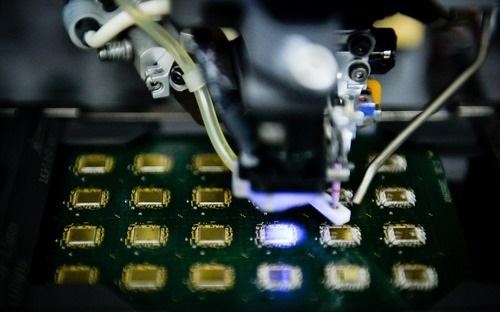

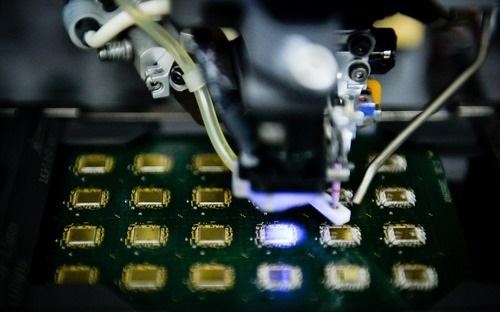

长电科技组装车间内芯片焊线

小芯片是一种芯片“模块化”设计方法,也是一种异构集成的封装技术。简单来说,小芯片能将不同工艺节点、不同功能,甚至不同材质的芯片,如同搭积木一样,通过先进封装技术集成在一起,从而形成一个系统级芯片(SoC),以平衡芯片计算性能与成本。与传统的SoC方案相比,小芯片模式具有设计灵活性、成本低、上市周期短三方面优势。目前台积电、高通等半导体企业,谷歌、微软等IT巨头在内的10家企业已经就小芯片技术展开广泛合作,公开了通用小芯片互联标准,还成立了产业联盟。

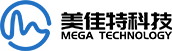

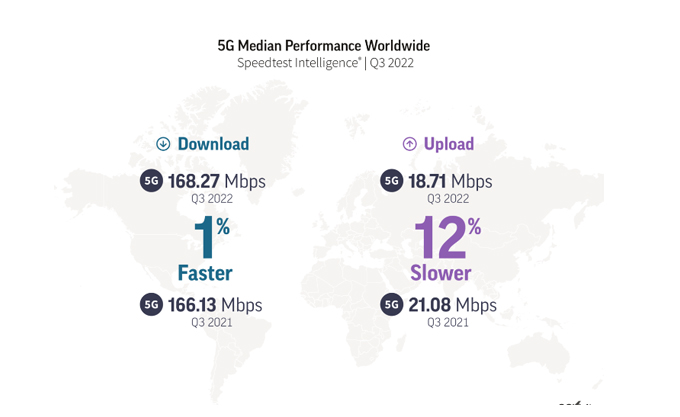

而长电科技的4 nm封装技术,与传统的3 nm制程技术相比,将有效地提高芯片的密度,大大降低对芯片制程的需求,同时长电科技还开发出了2D、2.5D和3D chiplet三种高密度集成方案,其中2D方案采用了特殊工艺来解决芯片内部应力问题,而2.5D方案则是用特殊加工方法来解决信号完整性问题。据介绍,长电科技将充分发挥XDFOI Chiplet工艺的技术优势,在高性能计算、人工智能、5G、汽车电子等领域应用,向下游客户提供外形更轻薄、数据传输速率更快、功率损耗更小的芯片成品制造解决方案。

近日,中国最大、世界第三大封测公司长电科技宣布,XDFOI Chiplet工艺已经实现了突破,并开始逐步进入稳定量产阶段,同步实现国际客户4nm节点多芯片系统集成封装产品出货,最大封装体面积约为1500mm2的系统级封装。该公司所研发的高密度多维异构集成系列工艺可以在有限的面积内,实现高密度的工艺集成,从而让芯片的封装尺寸更小,且性能更强。

众所周知,国内工业化起步较晚,在一些先进设备和技术上落后于西方等先进国家,尤其是在芯片制造领域,EUV光刻机是限制我国先进制程芯片发展的关键。不过当芯片制造进入3nm制程后,摩尔定律就越来越难以突破,加之半导体设备的技术竞争激烈,光刻机等设备价格与制造成本皆快速飙高,让业界被迫寻找新的替代技术,小芯片就是其中一个重要方向,同时也是中国市场换道超车的重要技术路径之一。

长电科技组装车间内芯片焊线

小芯片是一种芯片“模块化”设计方法,也是一种异构集成的封装技术。简单来说,小芯片能将不同工艺节点、不同功能,甚至不同材质的芯片,如同搭积木一样,通过先进封装技术集成在一起,从而形成一个系统级芯片(SoC),以平衡芯片计算性能与成本。与传统的SoC方案相比,小芯片模式具有设计灵活性、成本低、上市周期短三方面优势。目前台积电、高通等半导体企业,谷歌、微软等IT巨头在内的10家企业已经就小芯片技术展开广泛合作,公开了通用小芯片互联标准,还成立了产业联盟。

而长电科技的4 nm封装技术,与传统的3 nm制程技术相比,将有效地提高芯片的密度,大大降低对芯片制程的需求,同时长电科技还开发出了2D、2.5D和3D chiplet三种高密度集成方案,其中2D方案采用了特殊工艺来解决芯片内部应力问题,而2.5D方案则是用特殊加工方法来解决信号完整性问题。据介绍,长电科技将充分发挥XDFOI Chiplet工艺的技术优势,在高性能计算、人工智能、5G、汽车电子等领域应用,向下游客户提供外形更轻薄、数据传输速率更快、功率损耗更小的芯片成品制造解决方案。