PCIe TX/RX 物理层信号完整性测试方法详解

PCIe 既有串行通信接口,又有存储接口,这 一点与 SAS 和 SATA 不同,因此实现了额外 的行业扩充能力。PCIe 在跟复合 ( 系统 / 主机 ) 与端点 ( 插件 ) 之间基于点到点总线拓扑,支持全双工通信。这些规范是由 PCI-SIG 开发和维护的,这是 一家由 900 多家公司组成的协会。

PCIe 物理层包括:

● 差分低压 100 MHz 基准时钟

● 可 以 扩 充 通 路 宽 度:x1, x2, x4, x8, x12, x16, x32

● 可 以 扩 充 速 度:2.5GT/s (Gen1), 5GT/s (Gen2), 8GT/s (Gen3), 16GT/s (Gen4)

● 在一致性测试中使用不同的连接器,如 CEM、U.2 (SFF-8639)、M.2 或直接焊接到 PCB。

PCI Express— 它用在哪里?

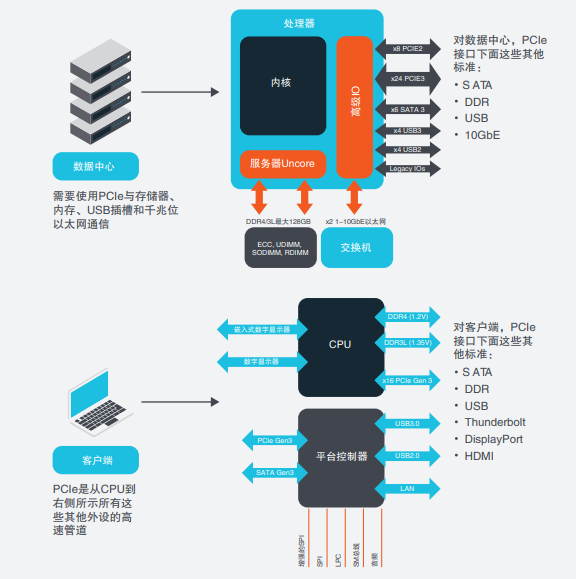

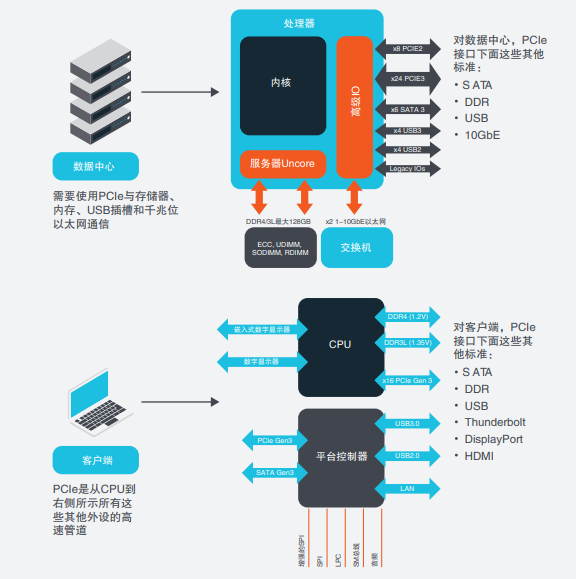

PCIe 是数据中心和客户端应用中使用的主要的新兴高性能存储和串行总线。PCIe 在外设之间实现了数据通信。 数据中心应用和客户端应用都有一个核心处理器, 为主机系统上的架构提供原始处理能力。这两种应用还必须接口各种外设器件,如 SATA 驱动器、 USB 设备等。在跟复合主机与端点器件之间,通常有许多路长损耗通道和连接器,带来了噪声、串扰、 定时不规则特点和其他损伤。因此,客户端和数据中心侧的 PCIe 器件必须能够可靠地演示 PCI 规定的一致性,补偿损伤,与 PCIe 器件互操作。

PCIe Gen4 最新进展

由于业界需要提高数据吞吐量和带宽吞吐量,因此 PCIe 数据速率必须提高,以跟上需求发展步伐。所以 Gen4 中最大的变化之一,是数据速率提高了 2 倍,从 Gen3 的 8GT/s 提高到 Gen4 的 16GT/s。

PCI Express 外形

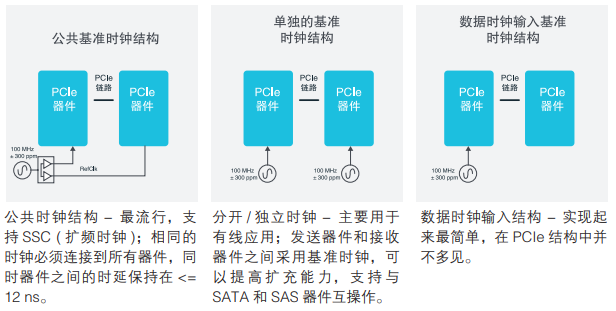

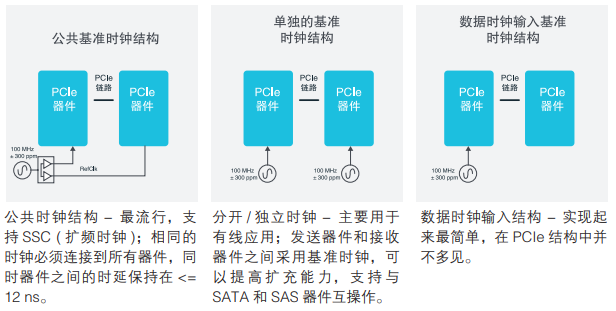

为了方便发射器件和接收器件可靠地传输数据,PCI-SIG 对基准时钟提出了非常严格的要求。标准规定使用 100 MHz 时钟 (Refclk),发射器件和接收器件上的频率稳定性大于 ±300 ppm,并支持三种不同的时钟结构,同时协调根复合芯片和端点芯片。

一致性测试预置值

为通过一致性测试,实现互操作,每台器件都要求进行 PCI-SIG 认证,它基于一个预置值或发射机均衡设置列表,从每秒 2.5 Gb/s 的低 数据速率直到最新的 16 Gb/s 的高数据速率。这些预置值用来均衡通道损耗,优化链路上的信号完整性。每个预置值都是主机应用到端 点的下冲和去加重的具体组合。

基本规范发射机 (Tx) 测试

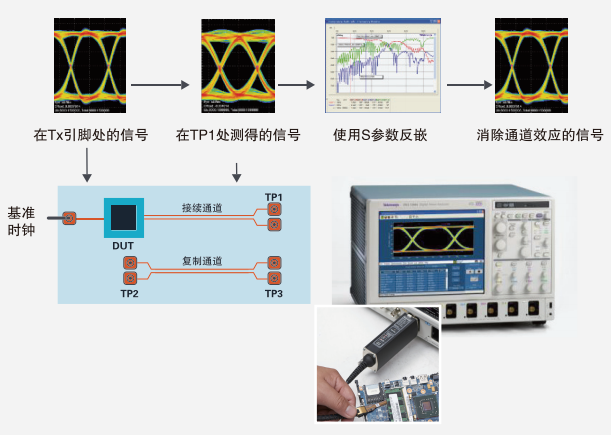

3. 使用高带宽探头,探测位置应尽可能靠近发射机引脚 。

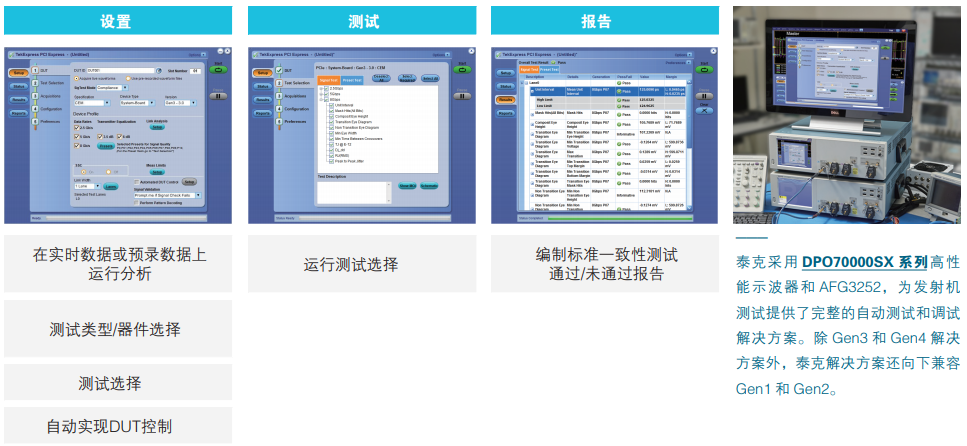

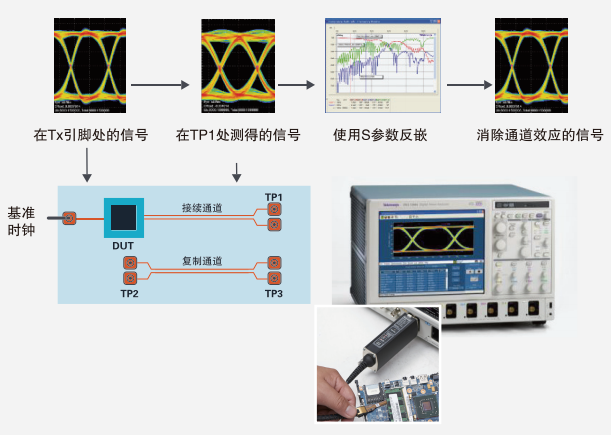

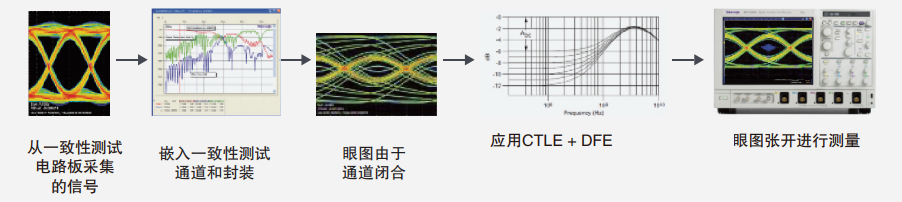

示波器可以使用 SDLA、Seasim 和 SigTest 之类 的软件工具,执行嵌入 / 反嵌、均衡和眼图分析。这种软件级分析允许设计人员在试产前优化和调试芯片性能,节约时间、资金及全面调试。确保采用的测量系统足够灵活,能够测试和调试被测器件的特定功能。

CEM 和 U.2 规范发射机 (Tx) 测试

在芯片器件的基本发射机测试中,直接规定了发射机引脚上的测量项目。由于有时不可能接入引脚,因此应在尽可能靠近这个基准点的位置执行测量。

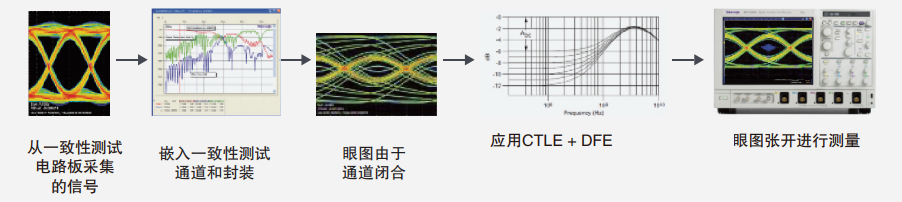

系统和插件在 CEM 级发射机测试中,会像接收机分片器看到的那样测量发射机的信 号完整性,但由于外形及测试过程中使用的夹具,不可能直接接入信号。为保证测量精度,应实现下面介绍了两个重要组件。

2. 使用软件工具应用通道均衡,测量和分析通道末端张开的眼图。PCISIG 提供了一个软件工具,称为 SIG-Test,应用与 PCI-SIG 特性有关的行为均衡器,提供测试通过 / 未通过结果。定制示波器软件,如泰克 DPOJET 和 SDLA,可以从闭上的眼图到张开的眼图,全面表征和调试均衡的信号。

接收机 (Rx) 测试基础知识

PCIe 测试和调试设置中的关键考虑因素

在您处理 Gen3 或 Gen4 PCIe 器件测试和调试前,要问以下几个关键问题:

PCIe 既有串行通信接口,又有存储接口,这 一点与 SAS 和 SATA 不同,因此实现了额外 的行业扩充能力。PCIe 在跟复合 ( 系统 / 主机 ) 与端点 ( 插件 ) 之间基于点到点总线拓扑,支持全双工通信。这些规范是由 PCI-SIG 开发和维护的,这是 一家由 900 多家公司组成的协会。

PCIe 物理层包括:

● 差分低压 100 MHz 基准时钟

● 可 以 扩 充 通 路 宽 度:x1, x2, x4, x8, x12, x16, x32

● 可 以 扩 充 速 度:2.5GT/s (Gen1), 5GT/s (Gen2), 8GT/s (Gen3), 16GT/s (Gen4)

● 在一致性测试中使用不同的连接器,如 CEM、U.2 (SFF-8639)、M.2 或直接焊接到 PCB。

PCI Express— 它用在哪里?

PCIe 是数据中心和客户端应用中使用的主要的新兴高性能存储和串行总线。PCIe 在外设之间实现了数据通信。 数据中心应用和客户端应用都有一个核心处理器, 为主机系统上的架构提供原始处理能力。这两种应用还必须接口各种外设器件,如 SATA 驱动器、 USB 设备等。在跟复合主机与端点器件之间,通常有许多路长损耗通道和连接器,带来了噪声、串扰、 定时不规则特点和其他损伤。因此,客户端和数据中心侧的 PCIe 器件必须能够可靠地演示 PCI 规定的一致性,补偿损伤,与 PCIe 器件互操作。

PCIe Gen4 最新进展

由于业界需要提高数据吞吐量和带宽吞吐量,因此 PCIe 数据速率必须提高,以跟上需求发展步伐。所以 Gen4 中最大的变化之一,是数据速率提高了 2 倍,从 Gen3 的 8GT/s 提高到 Gen4 的 16GT/s。

PCI Express 外形

为了方便发射器件和接收器件可靠地传输数据,PCI-SIG 对基准时钟提出了非常严格的要求。标准规定使用 100 MHz 时钟 (Refclk),发射器件和接收器件上的频率稳定性大于 ±300 ppm,并支持三种不同的时钟结构,同时协调根复合芯片和端点芯片。

一致性测试预置值

为通过一致性测试,实现互操作,每台器件都要求进行 PCI-SIG 认证,它基于一个预置值或发射机均衡设置列表,从每秒 2.5 Gb/s 的低 数据速率直到最新的 16 Gb/s 的高数据速率。这些预置值用来均衡通道损耗,优化链路上的信号完整性。每个预置值都是主机应用到端 点的下冲和去加重的具体组合。

基本规范发射机 (Tx) 测试

3. 使用高带宽探头,探测位置应尽可能靠近发射机引脚 。

示波器可以使用 SDLA、Seasim 和 SigTest 之类 的软件工具,执行嵌入 / 反嵌、均衡和眼图分析。这种软件级分析允许设计人员在试产前优化和调试芯片性能,节约时间、资金及全面调试。确保采用的测量系统足够灵活,能够测试和调试被测器件的特定功能。

CEM 和 U.2 规范发射机 (Tx) 测试

在芯片器件的基本发射机测试中,直接规定了发射机引脚上的测量项目。由于有时不可能接入引脚,因此应在尽可能靠近这个基准点的位置执行测量。

系统和插件在 CEM 级发射机测试中,会像接收机分片器看到的那样测量发射机的信 号完整性,但由于外形及测试过程中使用的夹具,不可能直接接入信号。为保证测量精度,应实现下面介绍了两个重要组件。

2. 使用软件工具应用通道均衡,测量和分析通道末端张开的眼图。PCISIG 提供了一个软件工具,称为 SIG-Test,应用与 PCI-SIG 特性有关的行为均衡器,提供测试通过 / 未通过结果。定制示波器软件,如泰克 DPOJET 和 SDLA,可以从闭上的眼图到张开的眼图,全面表征和调试均衡的信号。

接收机 (Rx) 测试基础知识

PCIe 测试和调试设置中的关键考虑因素

在您处理 Gen3 或 Gen4 PCIe 器件测试和调试前,要问以下几个关键问题: